Това е сравнително тиха международна суперкомпютърна конференция на хардуерния фронт, като обичайните заподозрени не обявяват нови процесори или ASIC за комутатори. Докато Триш Дамкрогер, генерален мениджър на подразделението за високопроизводителни изчисления на Intel, изнесе основната бележка за откриването на ISC 2021, предоставяйки малко повече информация за процесора Xeon SP „Sapphire Rapids“ и GPU ускорителя „Ponte Vecchio“, който предстои следващата година, започвайки с „Aurora“ A21 exascale суперкомпютър в Argonne National Laboratory, повечето от захранванията и скоростите на тези чипове остават загадка.

Никой не е казал официално, че машината Aurora се е отклонила от ревизираната си дата на доставка в края на 2021 г., но това е подозрението, откакто Intel обяви пропуск в своя 7 нанометров процес, който се използва за гравиране на части от Ponte Vecchio GPU, известен също като Xe HPC устройство, миналия юли.

По това време планът беше да има Aurora на полето в Аргон до края на 2021 г., но това изглеждаше малко вероятно, като се има предвид, че тогавашният изпълнителен директор Боб Суон каза на Уолстрийт, че първоначалните доставки на Ponte Vecchio ще се проточат до края на 2021 г. до началото на 2022 г. Intel преразгледа плана на Ponte Vecchio, за да използва комбинация от чиплети, гравирани в собствените му леярни, както и тези на своите конкуренти, в този случай Taiwan Semiconductor Manufacturing Corp, която всъщност има работещ 7 нанометров процес за разлика от Intel и GlobalFoundries. (Samsung, единственият друг доставчик на 7 нанометрови чипове и партньор на IBM за Power10, работи по него.)

Damkroger не спомена, между другото, че Intel всъщност изтласква датата на доставка за процесора Sapphire Rapids Xeon SP, който се гравира с помощта на настройката Enhanced SuperFin на 10-нанометровия производствен процес на Intel. Но Лиза Спелман, генерален мениджър на Xeon and Memory Group в наскоро реорганизираната Intel, публикува публикация в блог, обясняваща забавянето на доставката на сървърния чип в сърцето на – е, по-скоро като продълговатия мозък от графичните процесори на Понте Векио правете по-голямата част от мисленето – системата Aurora. Сега и Sapphire Rapids, и Ponte Vecchio се подхлъзнаха и изглежда много малко вероятно Argonne да получи основните части на системата тази година.

Във всеки случай пропускът на Sapphire Rapids засяга повече клиенти, отколкото този на Ponte Vecchio, и сега изглежда, че Ponte Vecchio ще победи Sapphire Rapids на терена.

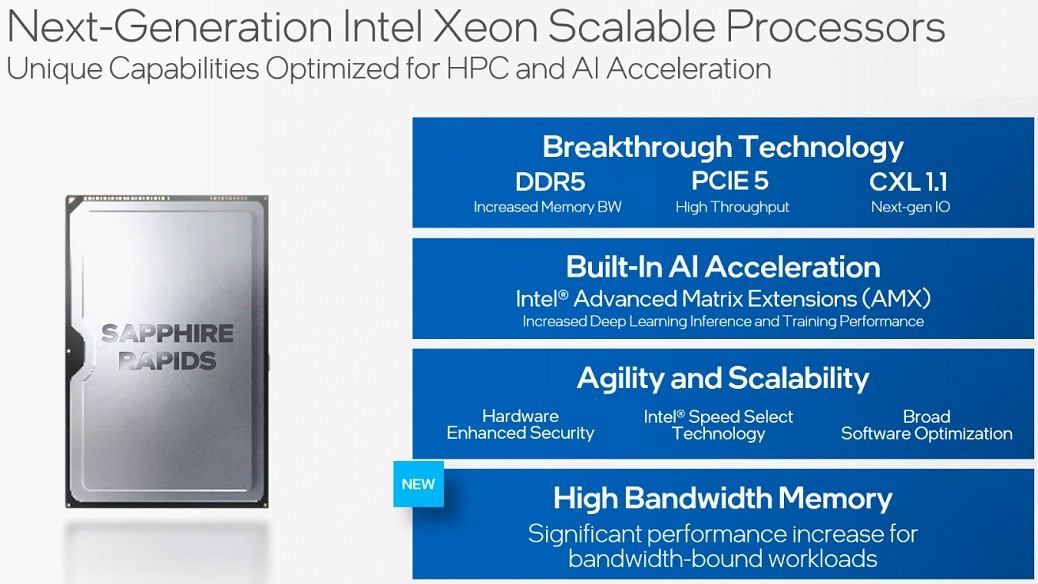

Чипът Sapphire Rapids е базиран на ядрото „Golden Cove“, което има нова микроархитектура, която включва два нови ускорителя, за които говори Спелман. Първият се нарича Advanced Matrix Extensions или AMX и подозираме, че това е матрично математическо наслагване върху векторните двигатели AVX-512, което повишава производителността на матричните операции, подобни на тези, извършвани от модулите Tensor Core на Nvidia GPU като както и матрични наслагвания за вектори в бъдещите чипове Power10 на IBM. Spelman не говори за AMX, но казва, че на ранния силикон за Sapphire Rapids изводите за машинно обучение и тренировъчните натоварвания се изпълняват 2 пъти по-бързо, отколкото на настоящите процесори Xeon SP „Ice Lake“, които просто предлагат смесена прецизност в своите векторни машини за повишаване на производителността на AI.

Друга предстояща функция в ядрото на Golden Cove – поне вариантът, насочен към сървъри – се нарича Data Streaming Accelerator, или DSA, и е проектирана за различни видове натоварвания с висока производителност, за да повиши и производителността при движение на поточно предаване на данни като операциите за преобразуване, които често се извършват за поточно предаване на данни в съхранение, работа в мрежа и аналитични натоварвания.

„Търсенето на Sapphire Rapids продължава да расте, докато клиентите научават повече за предимствата на платформата“, каза Спелман в съобщение в блог. „Като се има предвид широчината на подобренията в Sapphire Rapids, ние включваме допълнително време за валидиране преди производственото пускане, което ще рационализира процеса на внедряване за нашите клиенти и партньори. Въз основа на това сега очакваме Sapphire Rapids да бъдат в производство през първото тримесечие на 2022 г., като нарастването ще започне през второто тримесечие на 2022 г.“

Хората в AMD сигурно се кикотят и се кикотят. Вероятно и тези от Ampere Computing. Можем да чуем шегите „Sapphire Not So Rapids“ и „Ponte Vecchio Too Far“ отдалеч. . . .

Трудно е да се каже кога наследникът на сегашния „Ice Lake“ Xeon SP трябваше да излезе на пазара, защото самият Ice Lake се движи толкова много. Ice Lake беше отложено с около три години, когато стартира през март, така че трябваше да постави това, което стана Sapphire Rapids някъде 18 до 24 месеца след това. Наречете го март 2019 г., за да бъдете щедри. Това сега означава, че 10-нанометровите чипове все още изостават с три години след това забавяне и не са успели да ги наваксат. Надяваме се в името на Intel, че няма да има ново забавяне с Xeon SP „Granite Rapids“, който ще бъде гравиран със 7 нанометрови процеси. След забавянето през юли 2020 г. процесорите Granite Rapids Xeon SP се изплъзнаха до първата половина на 2023 г. в сравнение с очакваното пускане в началото на средата на 2022 г. Това е моментът, когато Sapphire Rapids сега настъпва.

Голямото разкритие на ISC 2021 беше, че ще има вариант на процесора Sapphire Rapids, насочен към работни натоварвания на HPC и AI, който ще включва HBM памет. „Sapphire Rapids ще излезе преди Sapphire Rapids с HBM, но приблизително в същата времева рамка“, казва Дамкрогер. „И всеки ще може да купи Sapphire Rapids с HBM. Можете да използвате HBM самостоятелно или можете да го използвате с DRAM. Това наистина е интересно развитие. И както каза Дамкрогер, това няма да бъде просто специална SKU, която само избрани клиенти могат да купуват. Въпросът е колко ще струва добавянето на HBM и колко производителност ще добави.

Има някои слухове за това как ще изглежда Sapphire Rapids с HBM, един от които можете да видите тук и който изглежда доста правдоподобен. В този доклад се казва, че чипът Sapphire Rapids има четири 15-ядрени плочки за изчисления, като едно ядро е деактивирано, вероятно за да увеличи ефективния добив. Така че максималният брой ядра на сокет ще бъде четири пъти по четиринадесет или 56 ядра, с възможен скок до 60 ядра, ако производителността от 7 нанометра стане добра.

Този подход е точно това, което IBM прави със своя чип Power10, който има 16 физически ядра и само 15 ядра се активират от самото начало, защото знаят, че добивите от 7-нанометровия процес на Samsung ще бъдат – как да го изразим ? – обезпокоителен. И преди да започнете, помнете, че с дизайните „Pascal“ и „Ampere GPU“, Nvidia направи същото със 7-нанометровите процеси на TSMC.

Не е ясно дали тези гнезда на Sapphire Rapids са направени от чиплети, което би означавало, че I/O и контролери на паметта са отделени от основните блокове, или са цели процесори, които са реализирани по многочипов начин, както направи AMD с „Naples“ Epyc 7001s и по-ранни Opterons преди много време и както прави IBM от Power5 през 2005 г. Има четири стека HBM2, така че всички те могат да имат собствена памет и тя може да бъде MCM, ако този доклад е правилен . Стековете HBM2 са четири високи с 16 GB капацитет, за общо 64 GB на гнездо. И това е напълно разумно количество основна памет за HPC и AI приложение, а с честотна лента от 1 TB/sec това също е доста разумно. Капацитетът на HBM може да бъде удвоен, според нас, до 128 GB доста лесно, но не евтино, със стек с височина осем. Не е ясно колко DDR5 памет ще адресира този сокет на Sapphire Rapids, но вероятно ще бъде поне 512 GB и вероятно 1 TB и може би дори 2 TB.

Чиповете от най-висок клас Sapphire Rapids се очаква да тежат 400 вата, включително тяхната HBM2 памет. Преди много време се шегувахме, че всички компютри ще изглеждат като графични карти в дългосрочен план. Това със сигурност е вярно за процесорите Fujitsu A64FX и NEC Aurora, използвани в HPC (това е различна Aurora), а в дългосрочен план можете да очаквате и HBM вариант на Epyc. Това всъщност може да е една от тайните на системите в екзамащаб, които отделът Cray на Hewlett Packard Enterprise изгражда за Министерството на енергетиката на САЩ.

Вече знаем, че Intel и HPE/Cray използват възел Sapphire Rapids с два сокета с шест GPU ускорителя Ponte Vecchio, свързани през шината PCI-Express 5.0, използвайки протокола CXL 1.1 към процесорите. Три GPU на CPU, точно като в суперкомпютъра „Summit“ в Националната лаборатория Oak Ridge, създаден от IBM и Nvidia.

GPU ускорителят Ponte Vecchio Xe HPC, показан на изображението в горната част на тази история, има 49 плочки и над 100 милиарда транзистора. Това е звяр и е включен и ранният силикон преминава през тестване и валидиране, според Damkroger, и тя също така спомена другите форм фактори, които ще бъдат налични, както можете да видите по-горе. Има подсистема с четири GPU, както е показано, базирана на Open Accelerator Module на Open Compute Project, както и подсистема с осем GPU, която не е показана, която вероятно също отговаря на спецификацията на OAM. Предполага се, че те ще имат съгласувани интерфейси през CXL между графичните процесори и към процесорите, използвайки PCI-Express 5.0 превключваща тъкан.

PREV: Закон за балансиране на 35 петабайта All-Flash

NEXT: Google прави сървърната математика с Tau Cloud инстанции